Toggle Flip Flop Timing Diagram

I have found that j k flip flop circuits are best analyzed by setting up input conditions 1s and 0s on a schematic diagram and then following all the gate output changes at the next clock pulse transition. The timing diagram in figure 3 15 view b shows the toggle input and the resulting outputs.

T Flip Flop Timing Diagram Fundamentals Of Logic Design Pages 351

Is flip flop a synchronous or an asynchronous.

Toggle flip flop timing diagram. And the combination j k 1 is a command to toggle the flip flop ie change its output to the logical complement of its current value. Welcome i would like to ask you for explain this timing diagrams. Construct timing diagrams to explain the operation of d type flip flops.

The t toggle or trigger flip flop. The timing diagram in figure 3 15 view b shows the toggle input and the resulting outputs. Edge triggered d type flip flops.

This results in the jk flip flop acting more like a t type toggle flip flop when both terminals are high. Jk flip flop timing diagram positive edge triggering. Counter design with t flip flops timing diagram.

Describe alternative forms of jk flip flops. If logic 1 is applied to both j and k the output toggles at the trailing edge of each clock pulse just like a toggle flip flop. Does the output of jk flip flop toggle continously.

Although this circuit is an improvement on the clocked sr flip flop it still suffers from timing problems called race if the output q changes state. Understand timing diagrams to explain the operation of jk flip flops. I got some assignments for reading timing diagrams and solved it but i am not sure if it is good.

Jk flip flop timing diagram. We will assume an initial condition t 0 of q being low and q being high. A timing diagram illustrating the action of a positive edge triggered device is shown in fig.

Although developed from the basic sr flip flop becomes a very versatile flip flop with many uses. February 13 2012 ece 152a digital design principles 25 counter design with t flip flops. A technique that really works well in the classroom for doing this is to project a schematic diagram on a clean whiteboard using an.

The jk flip flop augments the behavior of the sr flip flop jset kreset by interpreting the j k 1 condition as a flip or toggle command. Counter design with t flip flops state diagram 001 100 010 011 111 000 110 101. Toggle t flip flop.

It is therefore. A description of the jk and t flip flops along with some example timing diagrams showing how they work. Ask question 0.

We will assume an initial condition t 0 of q being low and q being high.

Jk Flip Flop And The Master Slave Jk Flip Flop Tutorial

Jk Flip Flop And The Master Slave Jk Flip Flop Tutorial

The Clocked T Flip Flop Timing Diagram

Flip Flop Basics Overview Truth Table Various Types

Flip Flop Basics Overview Truth Table Various Types

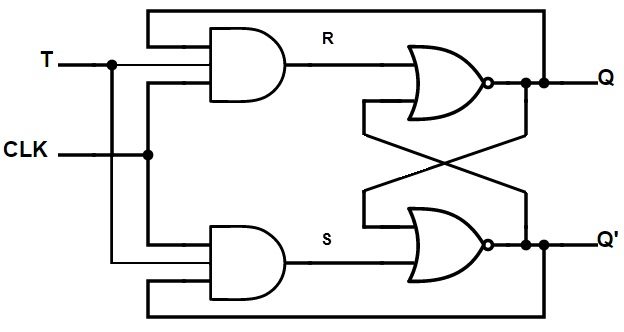

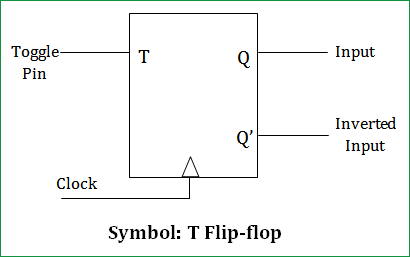

T Flip Flop Circuit Diagram Truth Table Working Explained

T Flip Flop Circuit Diagram Truth Table Working Explained

Elegant Of D Flip Flop Timing Diagram For An Asynchronous Youtube

Elegant Of D Flip Flop Timing Diagram For An Asynchronous Youtube

T Flip Flop Circuit Diagram Truth Table Working Explained

T Flip Flop Circuit Diagram Truth Table Working Explained

Flip Flop Circuits Digital Circuits Worksheets

Flip Flop Circuits Digital Circuits Worksheets

Frequency Division Using Divide By 2 Toggle Flip Flops

Frequency Division Using Divide By 2 Toggle Flip Flops

Flip Flops And Latches Northwestern Mechatronics Wiki

What Is The Problem Of S R Flip Flop How Can D Flip Flop Solve This

What Is The Problem Of S R Flip Flop How Can D Flip Flop Solve This

D Flip Flop Timing Diagram Finite State Machines Digsys Blog D

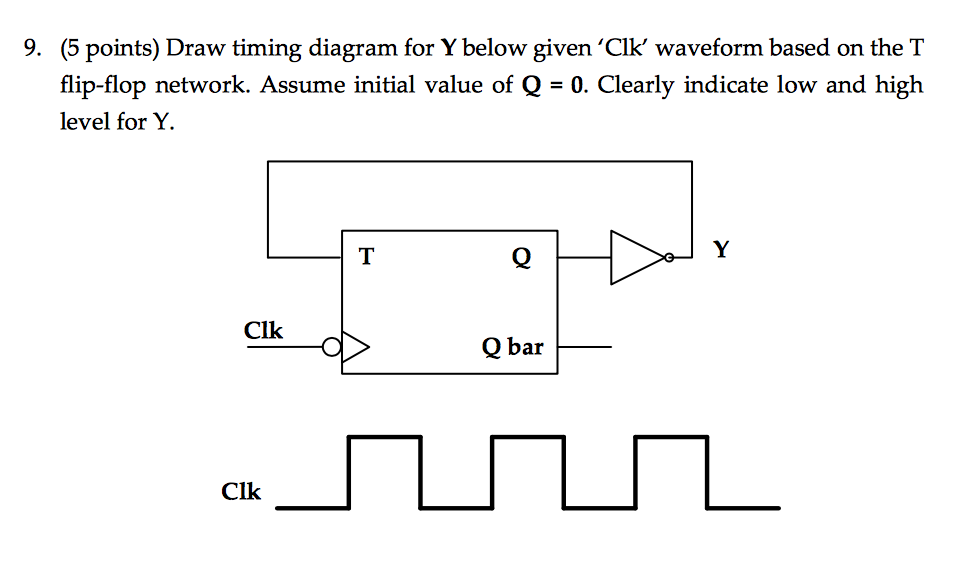

Solved Draw Timing Diagram For Y Below Given Clk Wavefo

Solved Draw Timing Diagram For Y Below Given Clk Wavefo

T Flip Flop Timing Diagram Vhdl Digsys Blog Air American Samoa

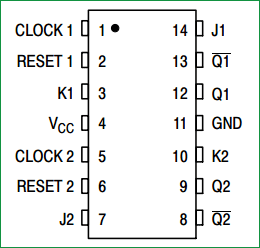

Collection T Flip Flop Circuit Diagram Solver Newest With Ic Of

Collection T Flip Flop Circuit Diagram Solver Newest With Ic Of

Rangkaian Sequensial Rs Flip Flop Jk Flip Flop T Flip Flop

Rangkaian Sequensial Rs Flip Flop Jk Flip Flop T Flip Flop

Engineering Timing Diagram Wiring Diagram

Solved Consider The Following Flip Flop Circuitcomplete The Ti

Solved Consider The Following Flip Flop Circuitcomplete The Ti

Types Of Flip Flop Circuits Explained Rs Jk D T

Types Of Flip Flop Circuits Explained Rs Jk D T

Solved 1 Assume The Initial Condition Of Qs Is 0 Comple

Solved 1 Assume The Initial Condition Of Qs Is 0 Comple

Flip Flops In Electronics T Flip Flop Sr Flip Flop Jk Flip Flop D

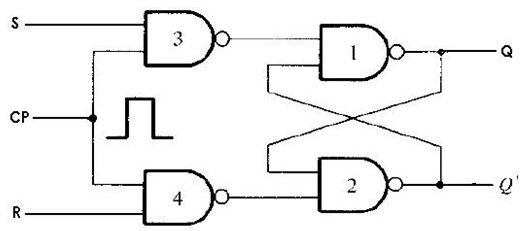

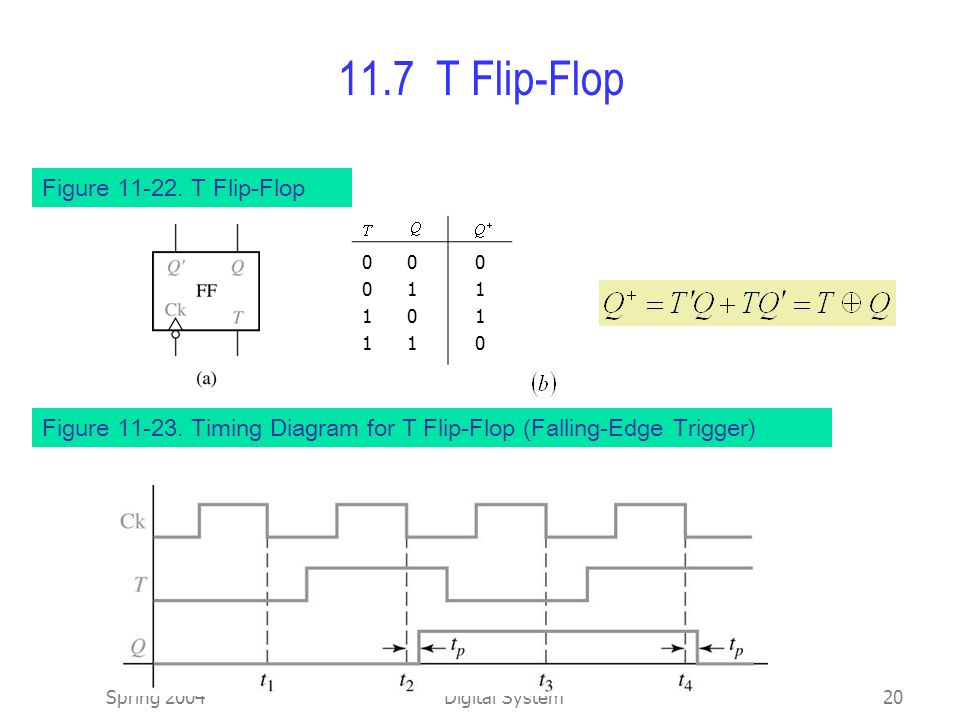

Chapter 11 Latches And Flip Flops This Chapter In The Book Includes

Chapter 11 Latches And Flip Flops This Chapter In The Book Includes

0 Response to "Toggle Flip Flop Timing Diagram"

Post a Comment